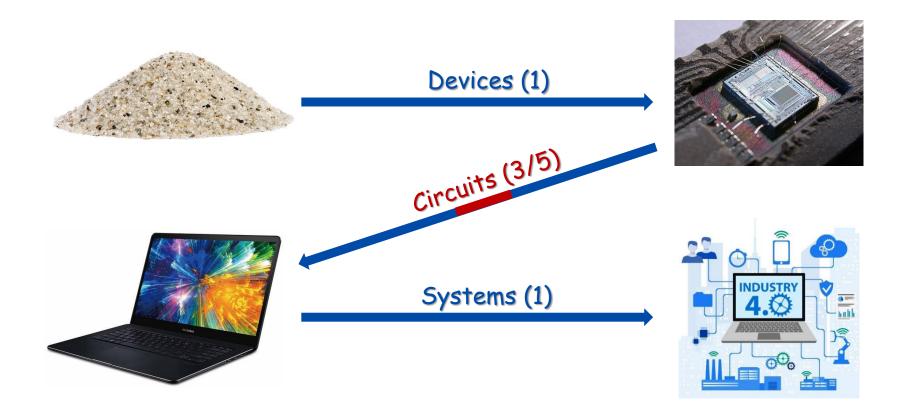

SI100B Introduction to Information Science and Technology (Part 3: Electrical Engineering)

Lecture #5 (Digital) Sequential Logic Circuits #2

Instructor: Haoyu Wang(王浩宇) Apr 18<sup>th</sup>, 2023

## The Theme Story

(Figures from Internet)

# Study Purpose of Lecture #5

- 哲学三问

- Who are you?

- Where are you from?

- Where are you going?

To answer those questions throughout your life

(Figures from Internet)

- In this lecture, we ask

- What is synchronous sequential circuit?

- How do we realize memory array?

- How to use finite state machine to build useful applications?

# Lecture Outline

- Synchronous sequential circuit

- The evolution of flip-flops

- Synchronous and asynchronous circuits

- Example: 4 x 3 memory

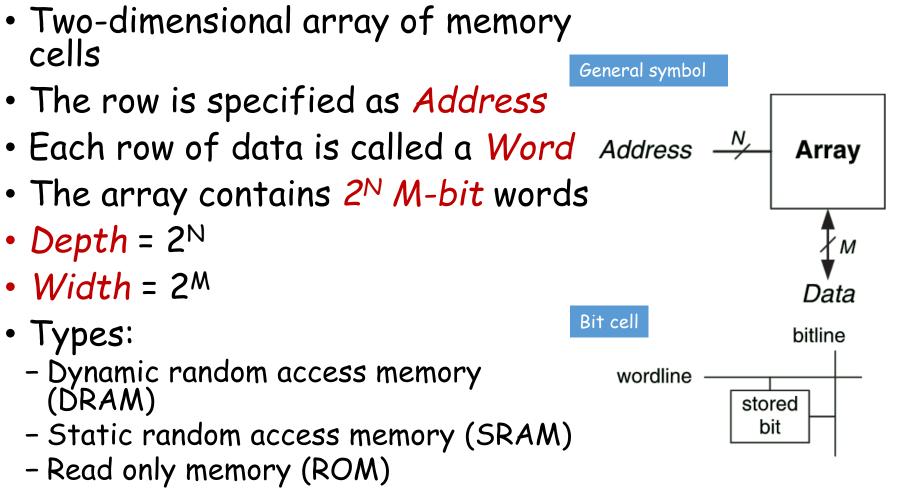

- Memory Array

- Finite state machines (FSM)

- Traffic light example

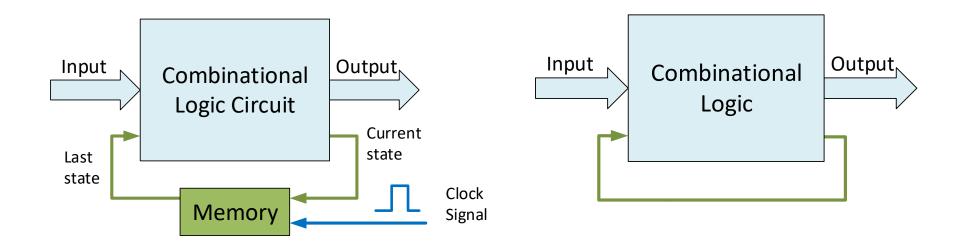

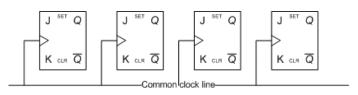

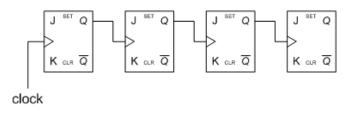

# Synchronous and asynchronous circuits

Synchronous circuit

Asynchronous circuit or self-timed circuit

# Synchronous and asynchronous circuits

Synchronous circuit

Asynchronous circuit or self-timed circuit

- Common clock signal

- Output only change at the edge of clock pulse

- clock signal should be long enough so that the critical path can settle before next clock edge

- Easy design

- Not governed by global clock

- Resulting state can be sensitive to the relative arrival times of inputs at gates, the race condition

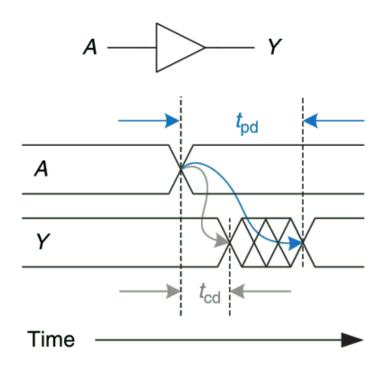

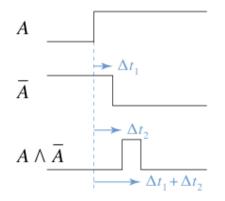

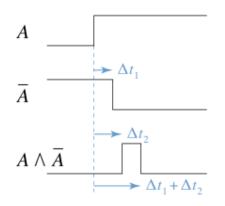

# Delay in combinational circuit

- contamination delay  $t_{cd}$

- Y (output) starts to change after the change of A (input)

- propagation delay t<sub>pd</sub>

Y (output) definitely

- settles in new value

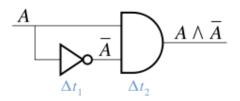

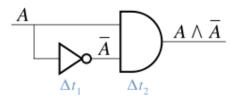

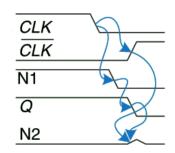

## Racing condition

• In combinational circuit

# Racing condition

• In combinational circuit

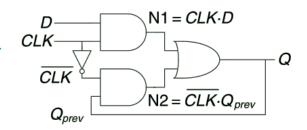

In asynchronous sequential circuit

- D = 1 CLK = 1;  $\overline{CLK}$  = 0  $Q_{prev}$  = 1\*1 + 0\*X = 1

- CLK = 1 → 0 ; CLK = 1 Q = 1\*0 + 1\*1 = 1

- Suppose the delay through the inverter from CLK to CLK' is rather long compared to the delays of the AND and OR gates

- eventually Q=0 because of the race condition

$Q = CLK \cdot D + \overline{CLK} \cdot Q_{prev}$

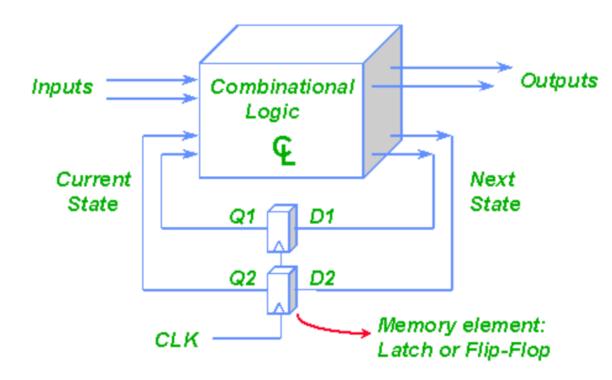

## Rules of synchronous sequential circuit

- Every circuit element is either a register or a combinational circuit

- At least one circuit element is a register

- All registers receive the same clock signal

- Every cyclic path contains at least one register

### Example: 2 x 2 memory

- 2 words and each can store 2 bits of information

- To represent 2 words need 1-bits for address

Address decoder performs the address decoding

- To store information we use D Flip-Flop for each bit (total 4, as each location as 2 bits and we have 2 total locations)

- Need select variable to chose if we want to read or write data and that is combined with clock signal (using some combinational logic)

- Also need some other combinational logic...

## Example: 2 x 2 memory

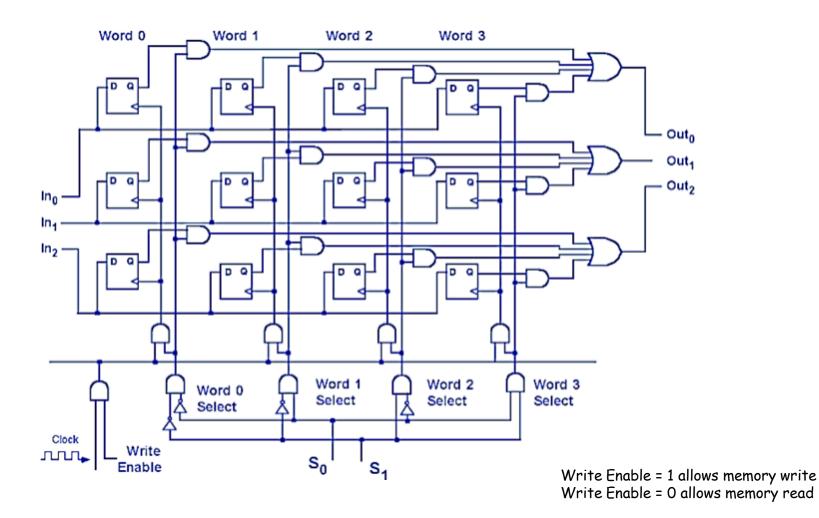

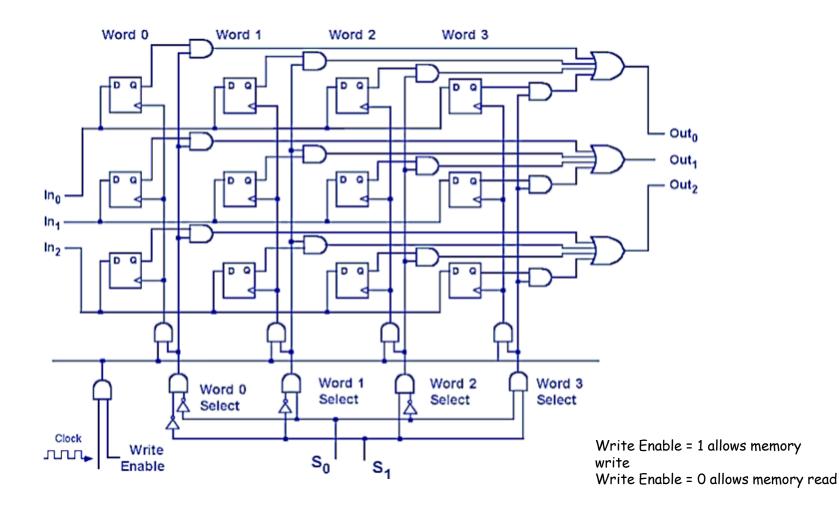

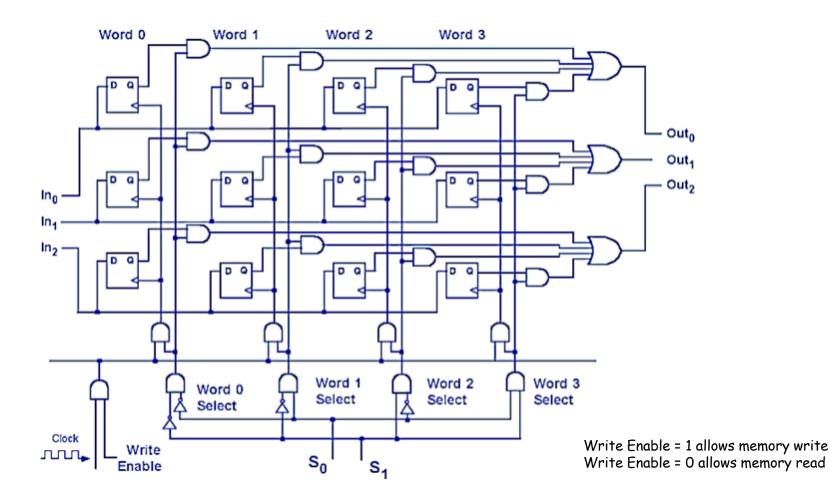

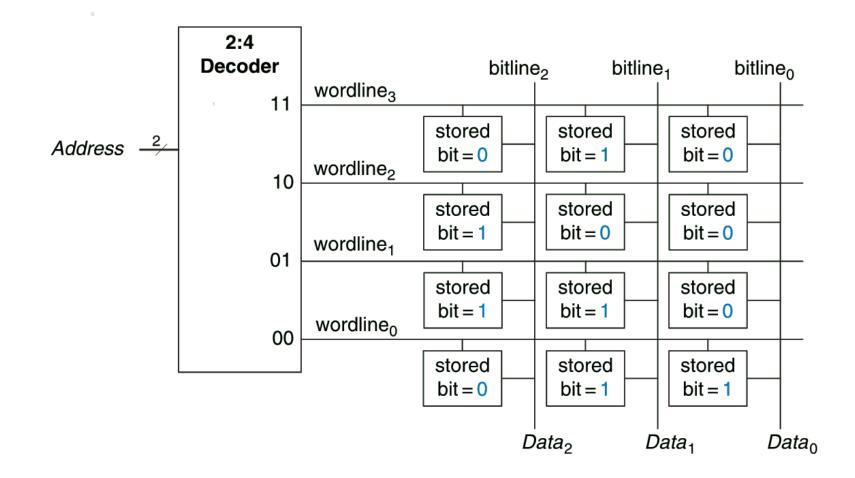

### Example: 4 x 3 memory

- 4 words and each can store 3 bits of information

- To represent 4 words need 2-bits for address

Address decoder performs the address decoding

- To store information we use D Flip-Flop for each bit (total 12, as each location as 3 bits and we have 4 total locations)

- Need select variable to chose if we want to read or write data and that is combined with clock signal (using some combinational logic)

- Also need some other combinational logic...

## Example: 4 x 3 memory

### Write operation to word 1

## Read operation from word 3

#### Memory array

- etc.

### Example: $4 \times 3$ Memory Array

## Volatile memory

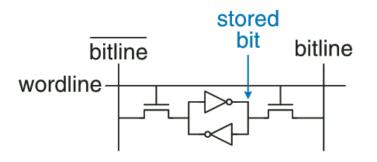

• Static Random Access Memory (SRAM)

Dynamic Random Access Memory (DRAM)

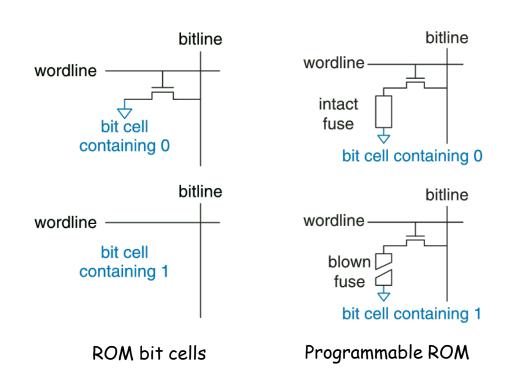

Nonvolatile memory

• Read only memory (ROM)

- Modern ROMs can be programmed (written) as well. For example flash memory

- Generally, ROMs take a longer time to write than RAMs, but are nonvolatile.

#### Memory comparison

The best memory type for a particular design depends on the speed, cost, and power constraints.

| Memory<br>Type                   | Transistors per<br>Bit Cell | Latency |

|----------------------------------|-----------------------------|---------|

| flip-flop                        | ~20                         | fast    |

| SRAM <mark>register cache</mark> | ' 6                         | medium  |

| DRAM main<br>memory              | 1                           | slow    |

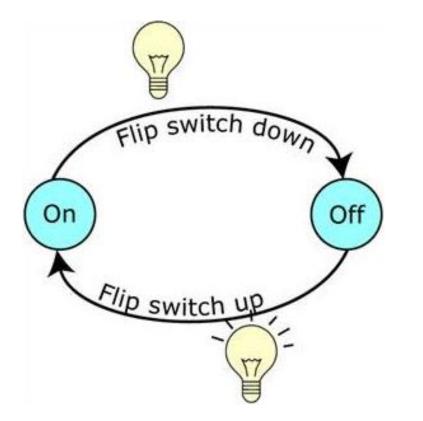

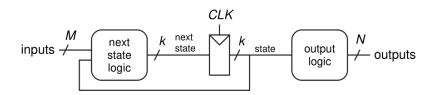

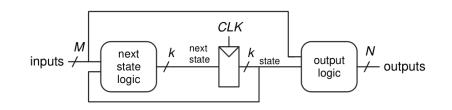

#### Finite-state machine

FSM - a mathematical model of computation used to design both <u>computer programs</u> and <u>sequential</u> <u>logic circuits</u>

#### The most seen FSM

#### Mealy machine

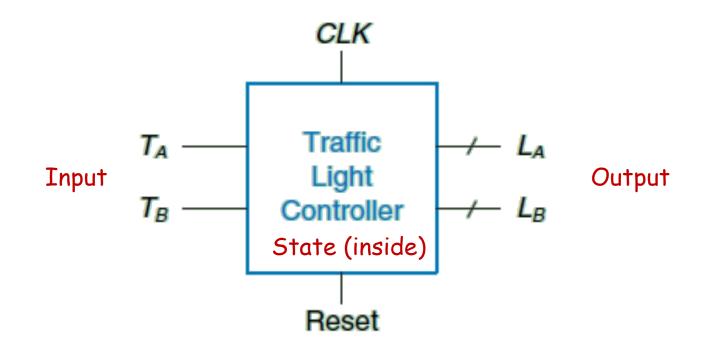

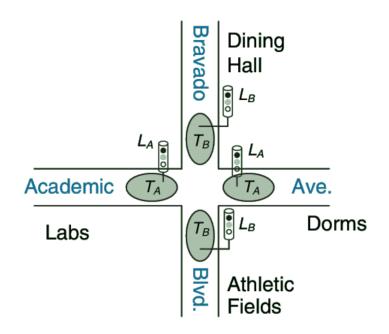

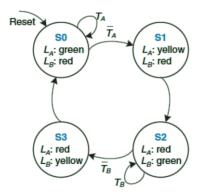

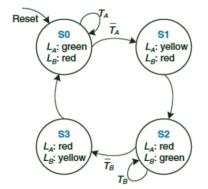

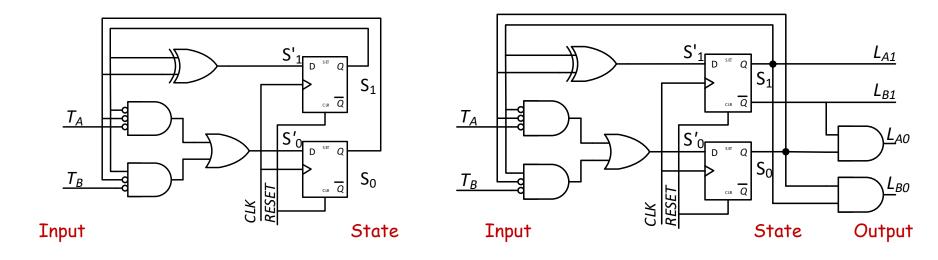

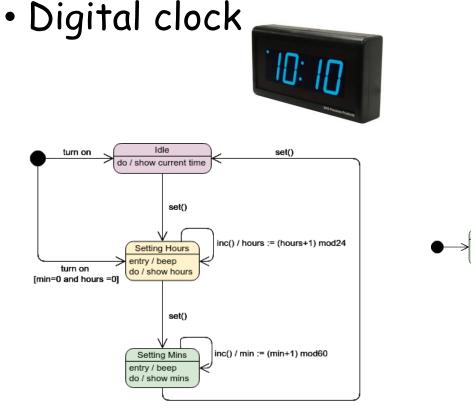

# Example: traffic light controller

- Traffic sensors  $T_A$  and  $T_B$ ("1" busy, "0" empty)

- Traffic lights  $L_A$  and  $L_B$ (each light have red, yellow, and green)

- 5-second clock, at each rising edge, lights may change based on the sensors

- Reset button

#### Black box view

SI100B Introduction to Information Science and Technology - Electrical Engineering - Lecture #5

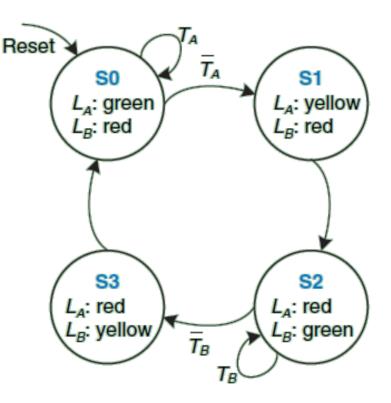

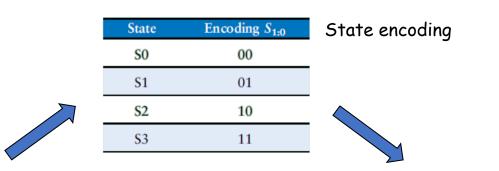

# State transition diagram

SI100B Introduction to Information Science and Technology - Electrical Engineering - Lecture #5

### State table

#### State transition table

| Current<br>State S | Inputs $T_A T_B$ |   | Next State<br>S' |

|--------------------|------------------|---|------------------|

| SO                 | 0                | х | <b>S1</b>        |

| <b>S</b> 0         | 1                | х | <b>S</b> 0       |

| <b>S1</b>          | х                | х | S2               |

| S2                 | Х                | 0 | \$3              |

| S2                 | Х                | 1 | S2               |

| \$3                | Х                | Х | S0               |

#### Binary encoded state transition table

| Current State         |                       | Inputs |                | Next State              |                                    |

|-----------------------|-----------------------|--------|----------------|-------------------------|------------------------------------|

| <b>S</b> <sub>1</sub> | <i>S</i> <sub>0</sub> | $T_A$  | T <sub>B</sub> | <i>S</i> <sub>1</sub> ' | <i>S</i> <sup>′</sup> <sub>0</sub> |

| 0                     | 0                     | 0      | х              | 0                       | 1                                  |

| 0                     | 0                     | 1      | х              | 0                       | 0                                  |

| 0                     | 1                     | х      | х              | 1                       | 0                                  |

| 1                     | 0                     | Х      | 0              | 1                       | 1                                  |

| 1                     | 0                     | Х      | 1              | 1                       | 0                                  |

| 1                     | 1                     | Х      | Х              | 0                       | 0                                  |

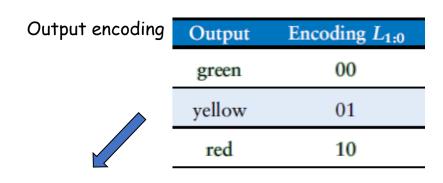

## Output table

Output table

| Curren                | t State    |                 | Out             | outs     |          |  |

|-----------------------|------------|-----------------|-----------------|----------|----------|--|

| <i>S</i> <sub>1</sub> | <b>S</b> 0 | L <sub>A1</sub> | L <sub>A0</sub> | $L_{B1}$ | $L_{B0}$ |  |

| 0                     | 0          | 0               | 0               | 1        | 0        |  |

| 0                     | 1          | 0               | 1               | 1        | 0        |  |

| 1                     | 0          | 1               | 0               | 0        | 0        |  |

| 1                     | 1          | 1               | 0               | 0        | 1        |  |

## Sum-of-product form

#### State table

| Curren<br>S <sub>1</sub> | it State<br>S <sub>0</sub> | Inputs<br>T <sub>A</sub> T <sub>B</sub> |   | Next $S'_1$ | State<br>S'0 |

|--------------------------|----------------------------|-----------------------------------------|---|-------------|--------------|

| 0                        | 0                          | 0                                       | Х | 0           | 1            |

| 0                        | 0                          | 1                                       | Х | 0           | 0            |

| 0                        | 1                          | Х                                       | Х | 1           | 0            |

| 1                        | 0                          | Х                                       | 0 | 1           | 1            |

| 1                        | 0                          | Х                                       | 1 | 1           | 0            |

| 1                        | 1                          | Х                                       | Х | 0           | 0            |

#### Output

| tab                   | e State               | Outputs         |                 |          |                 |

|-----------------------|-----------------------|-----------------|-----------------|----------|-----------------|

| <i>S</i> <sub>1</sub> | <i>S</i> <sub>0</sub> | L <sub>A1</sub> | L <sub>A0</sub> | $L_{B1}$ | L <sub>B0</sub> |

| 0                     | 0                     | 0               | 0               | 1        | 0               |

| 0                     | 1                     | 0               | 1               | 1        | 0               |

| 1                     | 0                     | 1               | 0               | 0        | 0               |

| 1                     | 1                     | 1               | 0               | 0        | 1               |

# State & output logic

- State logic (sequential)

- Output Logic (combinational)

### FSM with more states .....

Finite State Machine: Soda Machine State Diagram 25 Quarter Nickel 5 0¢ 5¢ 10¢ 15¢ 20¢ 25¢ 30¢ 35¢ 40¢ 45¢ 50¢ 55¢ Dime Dispense **Reset State**

# FSM with more states .....

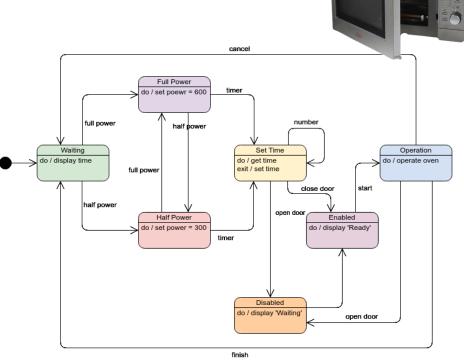

• Microwave oven